Транзисторные схемы

Транзисторные схемы работают достаточно похожим образом, и строятся на основе полевых транзисторов с изолированным затвором, так же известные как МОП-транзисторы (MOSFET), выполняющих роль переключателя. Однако, критерием “истинности” или “ложности” всей схемы является не протекающий ток, а значение напряжения (условно “высокое” или “низкое”)

Принципы работы полевых транзисторов

Полевые транзисторы состоят из двух полупроводниковых терминалов p- или n-типа (называемых исток (Source) и сток (Drain)), помещенных в субстрат соответственно n- или p-типа. N-тип соответствует электронной, а p-тип – дырочной проводимости. Сам транзистор обозначается по типу терминалов.

Так же присутствуют два терминала, называемых база (base) и затвор (gate), которые, собственно, и обеспечивают управление транзистором.

При приложении напряжения между базой и затвором, электроны или дырки притягиваются к области затвора, создавая канал проводимости между истоком и стоком. Изменение электрического поля между базой и затвором изменяет сопротивление этого канала.

Встречаются МОП-транзисторы с собственным (или встроенным) (depletion mode transistor) и индуцированным (или инверсным) каналом (enhancement mode transistor). Встроенный канал означает, что при нулевом напряжении затвор-база, канал транзистора открыт (т.е. проводит ток); для закрытия канала нужно приложить к затвору напряжение определенной полярности. Канал приборов с индуцированным каналом закрыт (не проводит ток) при нулевом напряжении затвор-база; для открытия канала нужно приложить к затвору напряжение определенной полярности. Полярность напряжения определяется типом проводников в транзисторе (N- или P-тип).

СИЗБNPPЗСИБ

Схема и условное обозначение PMOS с индуцированным каналом

СИЗБPNN

Схема и условное обозначение NMOS с индуцированным каналом

Схема и условное обозначение PMOS с собственным каналом

Схема и условное обозначение NMOS с собственным каналом

Часто терминал базы подключают напрямую к истоку.

Реализация логических операций на МОП-транзисторах

Независимо от типа транзистора, он может быть “настроен” таким образом, чтобы либо переходить в “открытое” состояние при подаче высокого напряжения (соответствующего логической единице) на затвор, либо низкого (соответствующего логическому нулю), и в “закрытое” в противном случае. При проектировании логических схем, имеет значение только этот фактор.

В этом контексте, транзисторы, переходящие в “открытое” состояние при подаче логической единицы на затвор, называются прямыми, а в “закрытое” – инверсными. При проектировании логики, часто используются следующие обозначения:

Прямой МОП-транзистор

Инверсный МОП-транзистор

Как правило, прямые транзисторы реализуются на NMOS, а инверсные – на PMOS.

На основе этих двух типов строятся микросхемы типа CMOS (КМОП – комплементарная структура металл-оксид-полупроводник, она же COS-MOS), состоящие из симметрично расположенных p- и n-канальных полевых транзисторов. Использование симметричных схем позволяет значительно уменьшить ток активации схемы, и снизить энергопотребление.

Штрих Шеффера может быть реализован, например, так:

VccF = A | BAB

Штрих Шеффера на прямых транзисторах

VccAVccBF = A | B

CMOS-схема штриха Шеффера

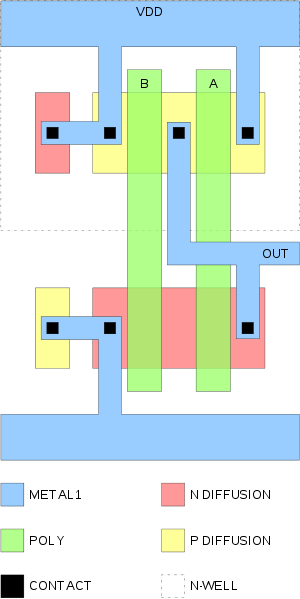

Физическое устройство CMOS-схемы

Физическое устройство CMOS-схемы

Логические схемы

На основе логических элементов строятся логические схемы. На логических схемах не рассматривается внутреннее устройство элементов, поэтому все логические схемы полностью эквивалентны логическим формулам, которые их выражают.

Для обозначения логических элементов, соответствующих базовым логическим операциям используются следующие обозначения:

&

Конъюнктор, соответствует операции конъюнкции.

1

Дизъюнктор, соответствует операции дизъюнкции.

Инвертор, соответствует операции инверсии.

И-НЕ (NAND), соответствует штриху Шеффера.

ИЛИ-НЕ (NOR), соответствует стрелке Пирса.

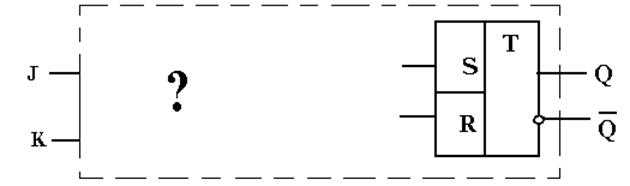

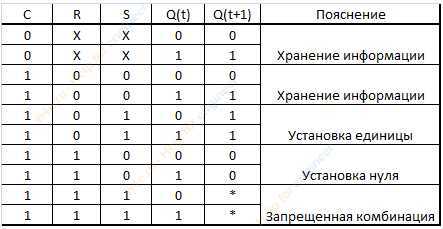

Устройство и принцип работы JK-триггера

Наиболее сложный по конструкции триггер широко используется в цифровой технике благодаря своей универсальности. Это, так называемый, JK-триггер.

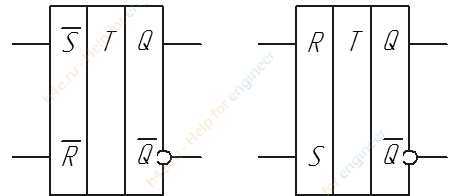

На рисунке видно, что JK-триггер имеет пять входов, в том числе прямой Q и инверсный выходы Q.

К уже известным входам R (Reset) – сброс, S (Set) – установка, С — тактовый вход добавлены ещё два. Это входы J (Jump) и K (Kill).

Благодаря наличию этих дополнительных входов появляется возможность несложными схемными средствами достигать интересных результатов.

Логика работы основных входов (C, J, K) реализована следующим образом. Если на входе J высокий потенциал, а на входе K – ноль, то триггер установится в единичное состояние по спаду тактового импульса на входе С. Если на входе J – ноль, а на входе К высокий потенциал то по спаду тактового импульса триггер «сбросится» в нулевое состояние. Когда J=K=0 независимо от тактовых импульсов состояние триггера не меняется. И если J=K=1, то при приходе каждого тактового импульса состояние триггера меняется на противоположное. В этом случае триггер работает как делитель частоты на два.

Благодаря такой логике работы появляется возможность довольно гибко настраивать алгоритм работы триггера. Такая универсальность позволяет использовать JK-триггер в устройствах со сложной логикой работы.

На JK-триггерах несложно реализовать делитель частоты на десять. Если мы подадим на вход импульсы с частотой 10 кГц, то на выходе получим уже 1 кГц. Такие схемы называют декадным делителем или декадой.

Делители с различным коэффициентом пересчёта раньше активно использовались радиолюбителями при изготовлении электронных часов и несложных музыкальных инструментов. Данная схема очень неэкономична и займёт много места, если собирать её на дискретных элементах, так как в ней используется четыре триггера и элемент 2И.

В широко распространённую серию К155 на базе ТТЛ логики входит универсальный JK-триггер К155ТВ1 (КМ155ТВ1). Зарубежными аналогами этой микросхемы являются SN7472N, 7472, SN7472J. Этот триггер построен по двухступенчатой схеме и имеет сложную входную логику, где три входа J и три входа K объединены по схеме логического И. Кроме того триггер имеет прямой и инверсный выходы, входы установки и сброса (S и R) и вход тактовых импульсов С. Вот так он обозначается на схеме.

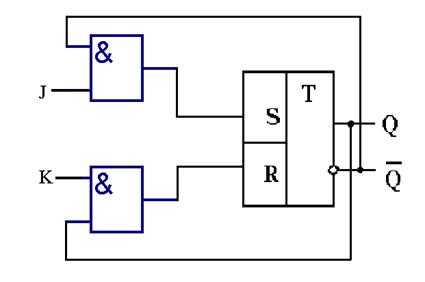

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

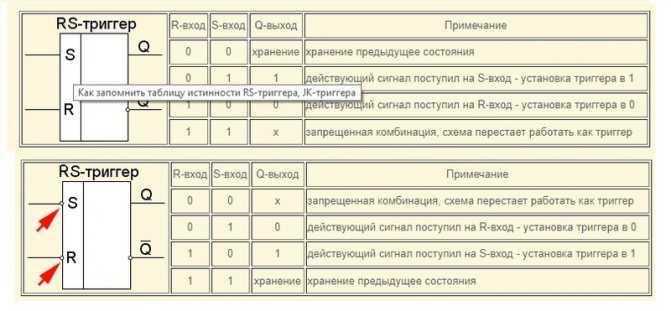

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Будет интересно Что такое электрическое поле: объяснение простыми словам

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

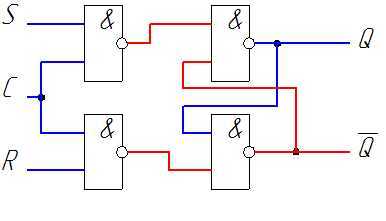

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

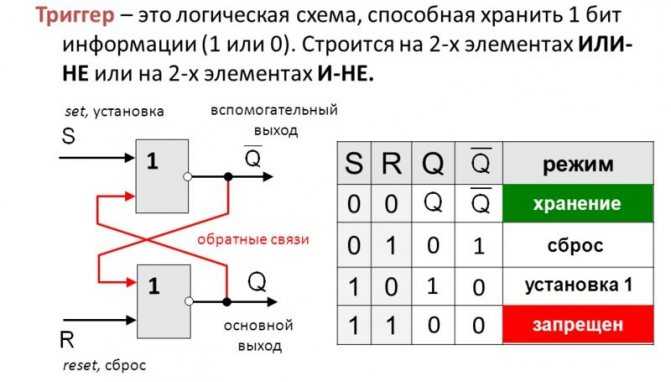

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

RS-триггеры

Логические устройства вычислительной техники

Что же такое RS-триггеры? В моем понимании — это устройства, которые могут принимать одно из двух состояний. На основании этого можно сделать вывод, что этот логический элемент может хранить один бит информации (грубо говоря, ноль или единицу). Существуют некоторые типы данного вида RS-триггеров. Давайте рассмотрим один из них:

Асинхронный RS-триггер

Имеет два входа “R» и «S” и два выхода, как правило это “Q” и “не Q” (т.е. инверсный) . Лично я запомнил, какой элемент для чего, после того, когда узнал, что R – это “RESET” (что означает “сброс”) и “S” – это “SET” (что означает установка)

Принимая во внимание изложенную информацию можно указать, что при подаче сигнала (единица) на “S” на выходе “Q” устанавливается единица, а при подаче единицы на “R” приводит к сбросу единицы на выходе “Q” и установки на нем нуля. Рассмотрим работу на базе элементов “2ИЛИ-НЕ” и “2И-НЕ”. Для этого используем графическое изображение этих элементов

Для этого используем графическое изображение этих элементов.

Итак, разберем принцип работы RS-триггера на базе элементов “2ИЛИ-НЕ”. В начальном положении, когда на R и S отсутствуют сигналы (логический “0”), на выходе “Q” присутствует также “0” или “1” – это исходное состояние. Выглядит это так:

Далее подадим на “S” логическуюединицу и получим на выходе “Q” также единицу. Будет выглядеть это так.

Следующим шагом подадим логическую единицу на “R” и уже на “Q” получим “0”. Изобразим это на рисунке.

Более наглядную работу RS-триггера на элементах 2ИЛИ-НЕ можно продемонстрировать, изобразив таблицу истинности. Вот так она выглядит.

Сейчас рассмотрим работу на элементах 2И-НЕ. Выглядит она аналогично, как и на элементах 2ИЛИ-НЕ с той лишь разницей, что активным уровнем является не “1”как в предыдущем случае, а “0”. Убедимся в этом, используя рисунок и таблицу истинности.

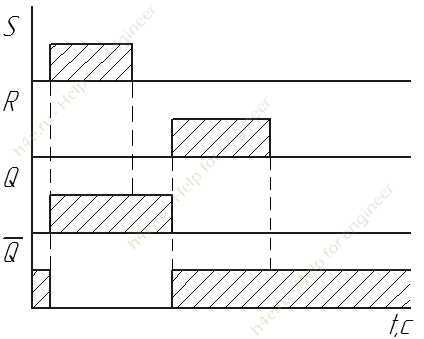

Асинхронным триггерам свойственно такое явление как присутствие “гонок”, что это? Это не одновременное или даже не согласованное по времени поступление информации на входы. Это приводит к наложению одного сигнала на другой. Чем это вызвано? А вызвано это разным временем быстродействия элементов, через которые проходит сигнал, прежде чем попасть на входы триггера, в данном случае на “R” или “S”. Покажем это явление на диаграмме.

Чтобы избавиться от этого явления, был придуман вариант подачи синхросигнала и асинхронный триггер превратился в синхронный.

Синхронные RS–триггеры

Этот вид логического устройства отличается от рассмотренного выше тем, что у него помимо входов “R” и “S” присутствует и третий “C”, на который подаются синхроимпульсы. Без этих импульсов информация на “R” и ”S” восприниматься не будет. Схему синхронного RS–триггера и диаграмму работы изобразим графически.

Из диаграммы видно, что в данном случае срабатывание происходит по переднему фронту (но бывает и по спаду) синхроимпульса.

Передний фронт синхроимпульса – это участок прямоугольного импульса, где происходит его возрастание.

Спад синхроимпульса – это участок спада синхроимпульса.

Именно здесь сделаем небольшое отступление и укажем, что бывают триггеры динамические и статические и соответственно со статическим и динамическим управлением. Чем они отличаются? Объясним максимально просто.

Динамические триггеры – на выходах, которых присутствуют либо непрерывная последовательность импульсов определенной частоты, либо ее отсутствие. (Напоминает управляемый генератор).

Статические триггеры– на выходах которых присутствуют неизменный уровень напряжения, либо его отсутствие.

Со статическим управлением – восприятие сигналов на информационных входах происходит только при подаче на “С” логической единицы (логического нуля).

С динамическим управлением – восприятие сигналов на информационных входах происходят в моменты перепада сигнала на “С”(Передний фронт синхроимпульса или спад синхроимпульса).

Если логические функции входов зависят от его выходов, то целесообразно использовать более рациональную конструкцию элементов.

Триггер RS типа

Одной из простейших в цифровой электронике является схема RS-триггера на транзисторах. Внешним воздействием на вход прибора можно установить его выход в нужное устойчивое состояние. Схема устройства представляет собой каскады, выполненные на транзисторах. Вход каждого из них подключается к выходу противоположного. Два состояния определяются присутствием на выходе напряжения, а переход между ними происходит с помощью управляющих сигналов.

Вам это будет интересно Виды, устройство и принцип работы ползункового реостата

Работает схема следующим образом. Если в начальный момент времени VT2 будет закрыт, тогда через сопротивление R3 и коллектор будет течь ток, поддерживающий VT1 в режиме насыщения. Одновременно первый транзистор начнёт шунтировать базу VT2 и резистор R4. Режим отсечки VT2 соответствует значению логической единицы на выходе Q = 1, открытое состояние VT1 нулю, Q = 0. Амплитуда сигнала на коллекторе закрытого ключа определяется выражением: Uз = U * R3 / (R2+R3).

Для инверсии сигнала необходимо на вход R или S подать импульс. При этом если S = 1, то и Q = 1, а если R=1, то на выходе будет ноль. При значениях R1 = R2 и R3 = R4 триггер называется симметричным. Особенностью работы устройства является способность удерживать установленное состояние между импульсами R и S, что и используется для создания на нём элементов памяти.

На схемах RS-триггер обозначается в виде прямоугольника с подписанными входами S и R, а также возможными состояниями выхода. Прямой подписывается символом Q, а инверсный – Q. Информация может поступать на входы непрерывным потоком или только при появлении синхроимпульса. В первом случае устройство называют асинхронным, а во втором – синхронным (трактируемым).

Работа устройства наглядно описывается с помощью таблицы истинности.

Она наглядно показывает всевозможные комбинации, которые могут возникнуть на выходе прибора. Такая таблица составляется отдельно для триггера с прямыми входами и инверсными. В первом случае действующий сигнал равен единице, а во втором — нулю.

Принцип работы RS-триггера

Триггер – это электронное устройство, которое предназначается для записи и хранения информации. Обычно он имеет два выхода: прямой и инверсный; и некоторое количество входов, в зависимости от выполняемой задачи. Под действием входных сигналов, изменяется состояние выходов. Напряжение на выходах изменяется резко – скачкообразно. Для изготовления триггеров обычно используются биполярные, униполярные транзисторы (полупроводниковые приборы).

Информация может записываться в триггеры свободно (непрерывно), то есть при подаче сигналов на вход, состояние выхода меняется в реальном времени. Такие триггеры называются асинхронными. А может информация записываться, только когда активен синхронизирующий сигнал. При отсутствии положительного уровня напряжении на нем, информация на выходах измениться не может – синхронные (тактируемые) триггеры.

RS-триггер именуется так из-за названия его входов:

| R – reset (сбросить); | ||

| S– set (установить). |

Он оснащен двумя входами, как говорилось, и двумя выходами:

| Q – прямой выход; | ||

| Q – инверсный. |

Асинхронный RS-триггер можно реализовать на логических элементах двумя схемами:

| — 2 «ИЛИ-НЕ»; | ||

| — 2 «И-НЕ». |

*Синий провод – «0», красный – «1»

Рисунок 1 – Схема асинхронного RS-триггера на логических «2ИЛИ-НЕ» элементах

Первая схема реализована на двух логических ИЛИ-НЕ, по рисунку 1 рассмотрим принцип работы приведенного RS-триггера.В нулевой момент времени, когда ни на один вход (R и S) не подана логическая единица, прямой выход Q=0, соответственно, инверсный =1. Если на вход S подать напряжение, уровень которого будет соответствовать единице, то выход Q скачкообразно изменит свое значение на 1, а на 0. Это произойдет запись информации. Если убрать единицу с “Set”, тогда выходы не изменят свое состояние, останутся такими, какими были – проявление свойства памяти. При подаче положительного сигнала на вход сброса, то есть R=1, инверсный выход резко станет равен 1, а прямой Q – 0. В работе RS-триггера есть недостаток: существует запрещенная комбинация. Нельзя одновременно подавать единичные сигналы на оба входа, нормальная работа триггера в этом случае невозможна.

Рисунок 2 — Схема асинхронного RS-триггера на логических «2И-НЕ» элементах

Вторая схема собрана с помощью двух логических элементов И-НЕ. Разница между ними заключается в том, что управление в прошлой схеме осуществлялось положительным сигналом (единицей), а в текущей активный уровень – ноль. Работают обе схемы идентично, поэтому описание принципа действия здесь не требуется.

Работу выше описанных устройств иллюстрирует временная диаграмма:

Рисунок 3 – Временная диаграмма RS-триггера

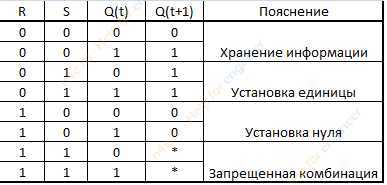

По вышеприведенному описанию работы триггера составим таблицу истинности («*» — невозможное состояние):

На схемах RS-триггер показывается как отдельное устройство, а не совокупность логических элементов, и имеет свое условное обозначение:

Рисунок 4 – Графическое обозначение асинхронного RS-триггера

Синхронный RS-триггер запоминает значения поданные на S или R вход, только при наличии единицы на С (Clock) сигнале – синхронизирующий или тактовый. Он позволяет избежать переходных процессов в схемах, а если быть точнее, переходных состязаний, когда один сигнал на вход может поступить раньше другого, и схема будет работать неправильно. Именно для этого предусмотрен синхронизирующий сигнал, который позволяет «включать» триггер в нужный нам момент времени.

Принцип действия синхронного RS-триггера легко понять по размещенному выше рисунку. Пока на вход С не подана единица, из-за наличия логических блоков ИЛИ, записываться сигналы с S или R входов не будут. При наличии 1 на входе С, работа синхронного триггера от асинхронного ничем не отличается. Составим таблицу истинности, где «крестиком» показывается невозможность записи сигнала, а «*» — запрещенная комбинация:

Графическое представление синхронного RS-триггера:

Триггеры: Методическое пособие по курсу «Цифровая техника и микропроцессоры», страница 3

R = 0 R = 1

Значит, состояние входа R для рассматриваемого перехода безразлично. Отразим это в первой строчке таблицы возбуждения прочерком в столбце R:

| Q(t) | S | R | Q(t+1) |

| — |

Переходам 0 -> 1 и 1 -> 0 соответствуют однозначные комбинации, а переходу 1 -> 1 — опять две, из которых вытекает безразличность состояния входа S. Заполнив все строки таблицы, получим окончательно таблицу возбуждения RS – триггера:

| Q(t) | S | R | Q(t+1) |

| — | |||

| 1 | 1 | ||

| 1 | 1 | ||

| 1 | — | 1 |

Эта таблица пригодится при синтезе триггеров других типов, а также цифровых автоматов.

1.2. Асинхронный JK – триггер

Нарушим общепринятую последовательность рассмотрения триггеров различных типов и рассмотрим синтез асинхронного JK-триггера, поскольку он является “старшим братом” RS-триггера ввиду большого сходства их таблиц истинности. Таблица истинности JK-триггера почти полностью совпадает с таблицей истинности RS-триггера и отличается лишь тем, что при подаче на входы комбинации «11» JK-триггер обязан переключиться в противоположное состояние.

Вот его таблица истинности (сравните с таблицей истинности RS-триггера):

Табл. 2.Таблица истинностиJK-триггера

| Q(t) | J | K | Q(t+1) | Действие |

| хранение | ||||

| 1 | сброс в 0 | |||

| 1 | 1 | установка в 1 | ||

| 1 | 1 | 1 | инверсия выхода | |

| 1 | 1 | хранение | ||

| 1 | 1 | сброс в 0 | ||

| 1 | 1 | 1 | установка в 1 | |

| 1 | 1 | 1 | инверсия выхода |

Разумно предположить, что JK-триггер может успешно заменять RS-триггер в любой цифровой схеме, причем вход J будет выполнять роль входа S, а вход K – роль входа R.

Пояснение

. Символы J и K не несут

никакой мнемоники и являются просто

последовательными буквами алфавита.

Получим логическое уравнение JK-триггера. Для этого заполним карту Карно и найдем МДНФ.

|

|

Это и есть логическое уравнение JK-триггера. Его полезно запомнить. Синтезируем базовую схему JK-триггера на основе уже имеющегося RS-триггера, поскольку RS-триггер является простейшей ячейкой хранения одного бита информации. Рассмотрим «черный ящик», на выходе которого стоит RS-триггер:

|

|

Вся будущая структура должна функционировать как JK-триггер. Поскольку на выходе стоит RS-триггер, то именно он определяет выходной сигнал, и, следовательно, обязан переключаться в соответствии с таблицей истинности JK-триггера. Для этого необходимо и достаточно сформировать на его входах S и R нужные сигналы для каждой строки таблицы.

Дополним таблицу истинности JK-триггера двумя столбцами для сигналов S и R и впишем в них нужные комбинации из таблицы возбуждения RS-триггера, чтобы обеспечить каждый переход вида Q(t) -> Q(t+1):

| Q(t) | J | K | Q(t+1) | Нужно подать |

| S | R | |||

| — | ||||

| 1 | — | |||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | |

| 1 | 1 | — | ||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | — | |

| 1 | 1 | 1 | 1 |

переходы

Эта расширенная таблица позволяет записать СДНФ для сигналов S и R, считая аргументами столбцы Q(t),J,K:

Теперь очевидна реализация JK-триггера:

Рис.2. Принцип

построения

JK-триггера

Следует заметить, что эта структура поясняет лишь принцип построения JK-триггера, в действительности она неработоспособна! Нетрудно догадаться, что при подаче сигналов J = K = 1 такой триггер превратится в автогенератор меандра, поскольку будет непрерывно изменять свое состояние на противоположное.

Поэтому на практике эту схему обычно выполняют двухтактной или вводят дополнительные элементы, превращающие выходную ступень в непрозрачный триггер, устраняя тем самым возможность паразитной автогенерации.

По таблице истинности легко составить таблицу возбуждения JK-триггера:

| Q(t) | J | K | Q(t+1) |

| — | |||

| 1 | — | 1 | |

| 1 | — | 1 | |

| 1 | — | 1 |

JK-триггер принято называть универсальным триггером. Это название отражает тот факт, что на его основе легко построить триггер любого другого типа. Признаком выполнения триггера по двухтактной схеме является наличие двух букв TT в правой части символа изображения триггера. Заметим, что принципиально выполнима задача взаимной трансформации триггеров любых типов.

1.3. Асинхронный Т-триггер (счетный триггер)

Поставим задачу синтезировать схему триггера, который инвертирует свое состояние каждый раз, когда на его единственном управляющем входе T

появляется уровень логической единицы. Наглядно это можно изобразить временной диаграммой, полагая в частном случае, что

Классификация

Энергия конденсатора

Изделия этой категории разделены на две основные группы по принципу сигналов управления. В первой – формируется заданная последовательность выходных сигналов, если установлено состояние «1». После переходе в «0» генерация прекращается. Вторая – способна переключать выходное напряжение соответствующим образом. Как правило, «1» примерно соответствует уровню источника питания.

Также триггеры различают по следующим параметрам:

- синхронность рабочих циклов;

- статические (динамические) способы управления;

- сложность логических схем;

- одно,- или двухступенчатые.

Триггеры на логических элементах и на операционном усилителе

Для реализации статических триггеров хорошо подходит схема усилителя с двумя каскадами. Связь между ними организуют прямую либо с ограничительными резисторами в соответствующих цепях.

Триггер на логических элементах

Триггер (Trigger) Шмитта

Изделия этой категории могут быть созданы с применением разной элементной базы. В данном разделе рассмотрен триггер Шмитта на транзисторах. Он управляется изменением аналогового сигнала. В зависимости от уровня напряжения, выполняется переключение состояния памяти в соответствующее положение «0» или «1».

Триггер Шмидта на транзисторах с подключенной нагрузкой

Нежелательные последствия триггеров

Большинство триггеров, с которыми мы сталкиваемся, являются нейтральными и практически никак не сказываются на качестве нашей жизни. Но некоторые могут вызывать нежелательные последствия, такие как:

- Утрата контроля над эмоциями . Под воздействием триггера можно совершить плохой поступок или обидеть человека.

- Подверженность чужому влиянию . Даже взрослый человек в определенных обстоятельствах может воспринимать другого человека как наставника и подвергаться его влиянию.

- Спонтанные покупки . Маркетологи часто используют акции, искусственный ажиотаж, ненастоящие скидки и прочие триггеры, заставляющие людей совершать ненужные покупки.

- Ухудшение здоровья . Сильные переживания могут оказывать заметное влияние на самочувствие, снижать иммунитет и даже приводить к развитию хронических заболеваний.

Триггер может стать опасной психологической ловушкой. Иногда человек попадает в неё самостоятельно, но бывает и так, что этими уязвимостями нашей психики стремятся воспользоваться всевозможные мошенники и махинаторы

Поэтому важно своевременно осознавать влияние триггера и избавляться от него всеми доступными способами